围绕芯片产业,武创院用三年时间,写下一个完整的创新故事。

两年前,武创院联合武汉大学刘胜院士团队成立芯片制造协同设计研究所,聚焦国家关键核心技术攻关,推动团队成果高效转化与产业孵化。

一年前,由武创院等300余家单位共建高端芯片产业创新发展联盟,覆盖半导体产业龙头企业200余家。

三年时间,武创院构筑起“一个研究所+一个联盟+一个公共服务平台”,三大载体形成强大合力,助力武汉芯片产业高质量发展。

本期一路“项”新,一起走进武创芯研。

一颗芯片从无到有,要经历设计、制造、封装等多个流程。

封装(Package),是把集成电路装配为芯片最终产品的过程。先进封装实际上已成为超越摩尔定律的关键赛道,是撬动半导体产业继续向前的重要杠杆。

相较上海、深圳等集成电路“重镇”,武汉在封装、设计领域的实力还有待加强,这是决定武汉集成电路产业能否实现持续高质量发展的关键所在。

“把论文写在祖国大地上,让实验室里的技术真正成为产业突围的底气——这是我们团队二十余年的执念。”武创院芯片制造协同设计研究所首席科学家刘胜院士的话语,道出了一群科研人的初心。

在武汉打造“世界存储之都”的关键节点,面对芯片制造协同设计领域的“卡脖子”困境,武创院与刘胜院士团队携手,在半导体产业的深水区劈波斩浪。

“看到国内企业拿着国外软件小心翼翼适配产线,遇到断供风险就慌了手脚,心里像压着块石头。”刘胜院士深耕芯片封装与可靠性领域二十余年,亲历了我国半导体产业被“卡脖子”的无奈。2018年起,国外对我国芯片产业的制约层层加码,80%以上的制造封装可靠性工业软件依赖进口,设计与制造“两张皮”的断层,让高端芯片自主研发举步维艰。

而芯片就像精密的摩天大楼,设计图纸再完美,工艺跟不上、协同不顺畅,终究成不了合格品。

2022年4月,武创院正式启动运行,瞄准科技成果转化的“最后一公里”和科技企业培育的“最初一公里”,在武汉这片产业沃土上搭建“政产学研金服用”一体化创新体系。2022年下半年,双方的初次接洽如“久旱逢甘霖”,从技术论证到规划落地,半年内数十轮密集沟通,没有客套话,只有“如何破解难题”的务实探讨。

▲武创院芯片制造协同设计研究所

建设方案专家咨询论证会

武创院芯片制造协同设计研究所成立,并以武创芯研科技(武汉)有限公司为实体让技术走出实验室。

公司副总经理、仿真部部长余帅说,双方秉持“需求导向、产业聚焦”的共识,决心要打造一套中国人自己的、自主可控的芯片制造协同设计工具链,为产业突围送上“金钥匙”。

“要做就做从零到一的突破,绝不走修修补补的捷径。”这是研发团队立下的誓言。芯片制造协同设计横跨量子力学、材料科学、软件工程等多个领域,要打破人才、资源、协同三大壁垒,难度堪比在“无人区”开路。

人才是第一资源。武创院以柔性用人机制为“磁石”,把高校里的算法科学家、企业中的工艺专家、科研院所的仿真工程师聚到一起。

▲项目评审会

“一开始大家‘语言不通’,物理学家谈机理,工程师聊代码,工艺师说实操,像在跨服交流。”团队成员笑称,武创院牵头建立的“技术翻译”机制,让不同领域的专家坐到同一张桌子上,把各自的“专业密码”转化为共同的“攻坚语言”。

资源是关键支撑。算法好不好用,得在产线上检验。武创院发挥平台链接资源的优势,帮忙对接小试、中试产线资源,让研发团队的模型能在真实产业环境中“淬火”。

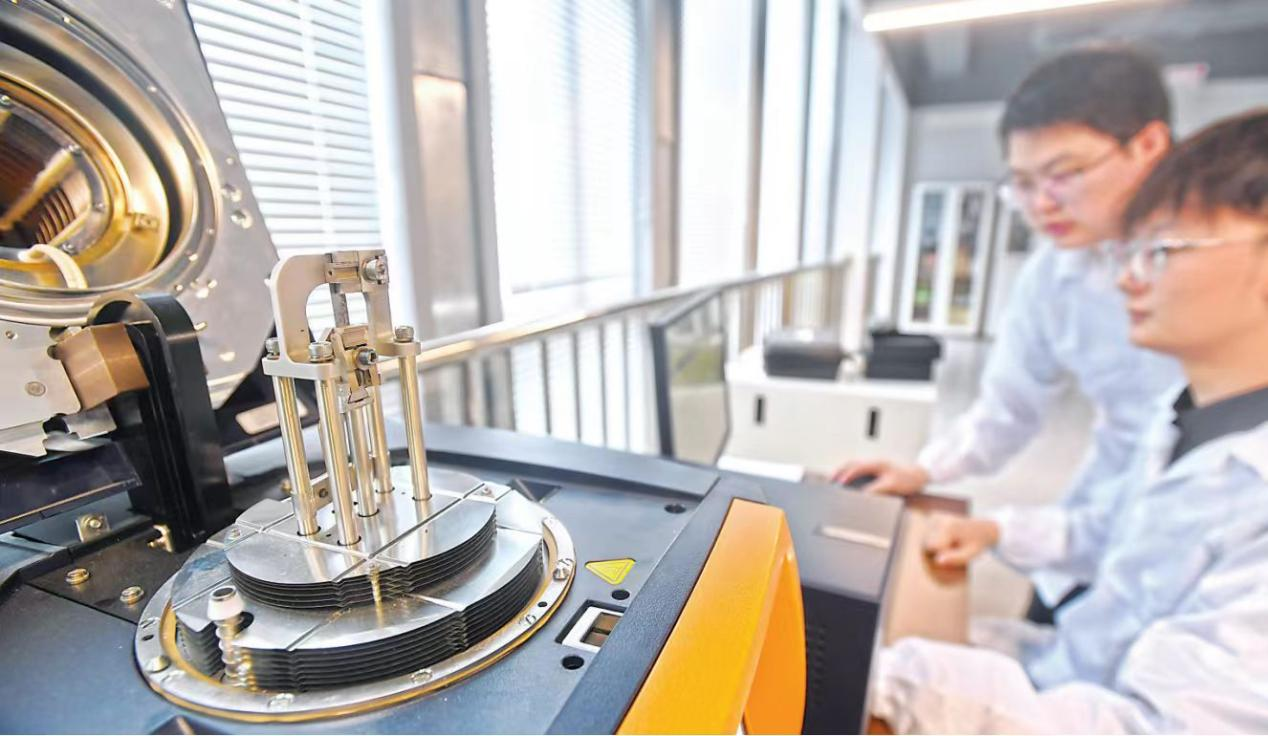

年轻的硕士、博士团队扎根实验室,白天对接企业需求,晚上熬夜优化算法,创新融合跨尺度与多物理场耦合算法,一点点搭建“机理-算法-软件-验证”的闭环体系。

▲武创芯研团队正在攻关

如今,十多个核心模块已完成初版研发,部分算法达到国际领先水平,过去需要三款国外产品才能实现的功能,现在一套自主工具就能搞定,企业使用成本大幅降低。

这背后,是无数个日夜的坚守,是跨领域协同的力量。

“技术好不好,企业说了算;价值高不高,应用见分晓。”在武创院的推动下,高端芯片产业创新发展联盟应运而生,一头连着研发端,一头连着长江存储、武汉新芯、长飞先进等300余家产业链企业,让创新需求“听得见”,技术成果“用得上”。

▲高端芯片产业创新发展联盟半导体材料专委会成立

某知名半导体企业曾被先进封装可靠性评估难题困扰,传统方法周期长、成本高。研发团队带着初版模块进驻企业,和对方技术人员同吃同住,一遍遍拆解工艺步骤,校准模型参数。

“一开始模拟结果和实际有偏差,我们没有互相推诿,而是一起找问题根源。”余帅回忆,历经数月数十次迭代,专用仿真模块终于落地,让企业产品可靠性评估周期缩短50%,上市节奏大幅加快。

“过去依赖国外软件,不仅贵,还得看别人脸色;现在用自主工具,响应快、适配性强,心里踏实。”合作企业技术负责人的评价,是对研发成果最好的肯定。如今,相关成果已服务于华为、中国电科等单位,在实践中持续优化升级,真正实现了“需求牵引研发,研发赋能产业”的双向奔赴。

从实验室到生产线,从技术突破到产业赋能,武创院芯片制造协同设计研究所书写着自主可控的“武汉答卷”,为我国半导体产业高质量发展不断注入新动能。

武创院芯片制造协同设计研究所

由中国科学院院士、武汉大学集成电路学院院长、工业科学研究院执行院长刘胜领衔,旨在突破半导体制造封装和可靠性工业软件“卡脖子”问题,部分成果已服务于华为和中国电科等单位。团队已打造代码自主率超90%的全流程国产仿真平台,核心求解器性能比肩ANSYS、ABAQUS,特定问题与行业顶级软件相比误差在1%以内。创新融合“量子力学—分子动力学—有限元”跨尺度算法与“热—力—流体—化学反应”多场耦合算法,精准覆盖半导体制造与封装关键工艺。构建“机理一算法一软件一验证”闭环体系,确保仿真真实可靠。依托项目建设了武创院芯片制造协同设计研究所,主导成立了高端芯片产业创新发展联盟,致力于搭建芯片产业链多方主体交流合作平台,服务覆盖长江存储、武汉新芯、长飞先进和九峰山实验室等300余家芯片龙头骨干企业。